The Engineering of Reliable Embedded Systems

The “Engineering of Reliable Embedded Systems” (ERES) documents an industry-proven approach to the development of software for reliable, real-time embedded systems, based on the use of time-triggered (TT) architectures.

The “Engineering of Reliable Embedded Systems” (ERES) documents an industry-proven approach to the development of software for reliable, real-time embedded systems, based on the use of time-triggered (TT) architectures.

- A comprehensive “Model-Build-Monitor” methodology for TT systems is presented.

- Modelling of TT systems is explored in detail, with numerous worked examples.

- Extensive (and complete) code examples are included.

- Run-time monitoring techniques are described in detail.

- Links to related international safety standards and guidelines are included throughout the text.

![]()

The techniques described in ERES have been applied successfully in designs ranging from household goods to industrial systems.

These techniques have proved to be of particular benefit to organisations that need to develop systems in compliance with international safety standards, such as IEC 61508, ISO 26262, DO-178C, IEC 62304, ISO 13849, IEC 60335 and IEC 60730, up to “SIL 2” level or equivalent.

Comments from the author

“I completed work on “Patterns for Time-Triggered Embedded Systems” around 15 years ago. Since then, I’ve probably worked on or advised on more than 200 ‘TT’ projects, and helped around 50 companies to make use of a TT approach for the first time. I’ve learned a great deal during this process. In “The Engineering of Reliable Embedded Systems”, I’ve done my best to encapsulate my experience in the development of reliable embedded systems using TT architectures.”

[Michael J. Pont, December 2014.]

![]()

Pre-order your copy of ‘ERES2’ today!

The second edition of ‘ERES’ (‘ERES2‘) will be published in June 2016.

Pont, M.J. (2016) “The Engineering of Reliable Embedded Systems (Second Edition)”, SafeTTy Systems.

ISBN: 978-0-9930355-3-1. £65.00.

Pre-order ERES2 on or before 29 April 2016 and pay just £35.00 (plus a delivery charge) for your copy.

This offer applies only to orders that are placed directly with SafeTTy Systems.

Payment can be accepted by PayPal® for book orders (or by bank transfer).

Please contact us for further information or to place your order.

![]()

![]()

Download sample chapters

![]()

Sample material from “ERES” is available for download here.

The extensive sample material includes drafts of the Preface and the first three chapters (in full), plus the detailed Table of Contents.

[Updated: Friday 23 January 2015.]

![]()

![]()

Download code examples

![]()

The team at SafeTTy Systems has developed an extensive set of “Time-Triggered Reference Designs” (TTRDs).

The TTRDs allow developers to implement a range of effective TT Platforms.

The TTRDs support the creation of effective task schedulers, robust tasks and comprehensive monitoring systems.

Developers can work with co-operative tasks sets or with designs that require task pre-emption.

The ERES book describes various TTRDs for the NXP® LPC1769 microcontroller in detail. These TTRDs target the readily-available (and low cost) LPCXpresso platform. You can download the LPC1769 TTRDs here.

The techniques described in ERES can be readily applied with numerous other microcontroller families: related TTRDs for devices from Texas Instruments®, STMicroelectronics®, Microchip Technology® and Silicon Laboratories® are available here.

All of our TTRDs are freely available for non-commercial use.

![]()

![]()

Table of Contents

![]()

Definitions

Acronyms and abbreviations

Reference designs

Preface

PART ONE: INTRODUCTION

CHAPTER 1: Introduction

CHAPTER 2: Creating a simple TTC scheduler

CHAPTER 3: Initial case study

PART TWO: CREATING RELIABLE TTC DESIGNS

CHAPTER 4: Modelling system timing characteristics

CHAPTER 5: Obtaining data for system models

CHAPTER 6: Timing considerations when designing tasks

CHAPTER 7: Multi-mode systems

CHAPTER 8: Task Contracts (Resource Barriers)

CHAPTER 9: Task Contracts (Time Barriers)

CHAPTER 10: Monitoring task execution sequences

PART THREE: CREATING RELIABLE TTH AND TTP DESIGNS

CHAPTER 11: Supporting task pre-emption

CHAPTER 12: Maximising temporal determinism

PART FOUR: COMPLETING THE SYSTEM

CHAPTER 13: Working with System Contracts

CHAPTER 14: Recommended system platforms

CHAPTER 15: Revisiting the case study

PART FIVE: CONCLUSIONS

CHAPTER 16: Conclusions

APPENDIX

APPENDIX 1: LPC1769 test platform

Full list of references and related publications

Index

![]()

![]()

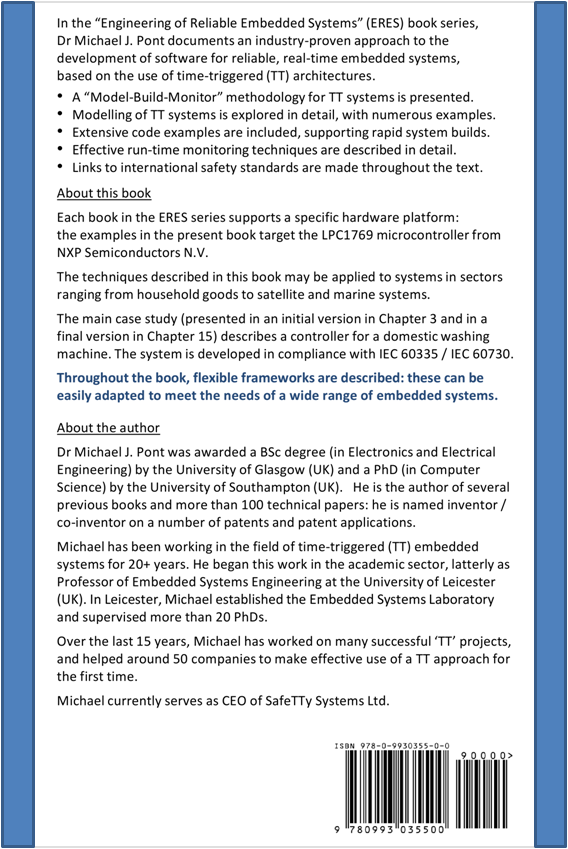

Back cover

![]()

![]()

![]()

ReliabiliTTy® Technology Licences

The books in the “Engineering of Reliable Embedded Systems” (ERES) series and the related Time-Triggered Reference Designs (TTRDs) describe patented technology and are subject to copyright and other restrictions.

The public TTRDs downloaded from this WWW site and the designs and techniques documented

in the ERES book series may be used without charge: [i] by universities and colleges in courses for which a degree up to and including “MSc” level (or equivalent) is awarded; [ii] for non-commercial projects carried out by individuals and hobbyists.

Use of the techniques and code examples described in the ERES books in any commercial project (including training courses) or in university research projects (including PhD-level programmes and equivalent) requires purchase of a ReliabiliTTy® Technology Licence.

![]()